# **SPECIFICATIONS**

|                                      | _ |

|--------------------------------------|---|

| CERTIFICATION : ROHS                 |   |

| DATE : <u>2009.03.02</u>             |   |

| DRAWING NO. :                        |   |

| SAMPLE CODE : <u>GFG128064A-FPGA</u> |   |

| CUSTOMER :                           |   |

| Customer Sign | Sales Sign | Approved By | Prepared By |

|---------------|------------|-------------|-------------|

|               |            |             |             |

|               |            |             |             |

|               |            |             |             |

|               |            |             |             |

# **Revision Record**

| Data(y/m/d) | Ver. | Description | Note | page |

|-------------|------|-------------|------|------|

| 2009.03.02  | 00   | New         |      | 18   |

|             |      |             |      |      |

|             |      |             |      |      |

|             |      |             |      |      |

|             |      |             |      |      |

|             |      |             |      |      |

|             |      |             |      |      |

|             |      |             |      |      |

|             |      |             |      |      |

#### **CONTENTS**

| 1. | SCO | PE                                               | <br>4 |

|----|-----|--------------------------------------------------|-------|

| 2. | PRO | DUCT SPECIFICATIONS                              | <br>4 |

|    | 2.1 | General                                          | <br>4 |

|    | 2.2 | Mechanical Characteristics                       | <br>4 |

|    | 2.3 | Absolute Maximum Ratings                         | <br>5 |

|    | 2.4 | Electrical Characteristics                       | <br>5 |

|    | 2.5 | Optical Characteristics Absolute maximum ratings | <br>5 |

|    | 2.6 | Optical Characteristics                          | <br>6 |

|    | 2.7 | LED Back-light Characteristics                   | <br>7 |

| 3. | REL | IABILITY                                         | <br>8 |

| 4  | OPE | R ATING INSTRUCTIONS                             | <br>9 |

|    | 4.1 | Input signal Function     | <br>9  |

|----|-----|---------------------------|--------|

|    | 4.2 | Voltage Generator Circuit | <br>10 |

|    | 4.3 | Timing Diagram            | <br>13 |

| 5. | NOT | TES                       | <br>16 |

| 6. | OPE | RATION PRECAUTIONS        | <br>16 |

| 7. | LCN | 1 DIMENSIONS              | <br>17 |

### 1. SCOPE

This specification covers the engineering requirements for the GFG128064A-FPGA liquid crystal module.

### 2. PRODUCT SPECIFICATIONS

- 2.1 General

- 128 \$64 dot matrix LCD

- FSTN, Positive mode LCD panel

- Transflective, Normal temperature type

- 6 o'clock

- Back light: Edge LED (BLUE)

- Multiplexing driving: 1/65duty, 1/9bias

- Conteroller IC UC1601

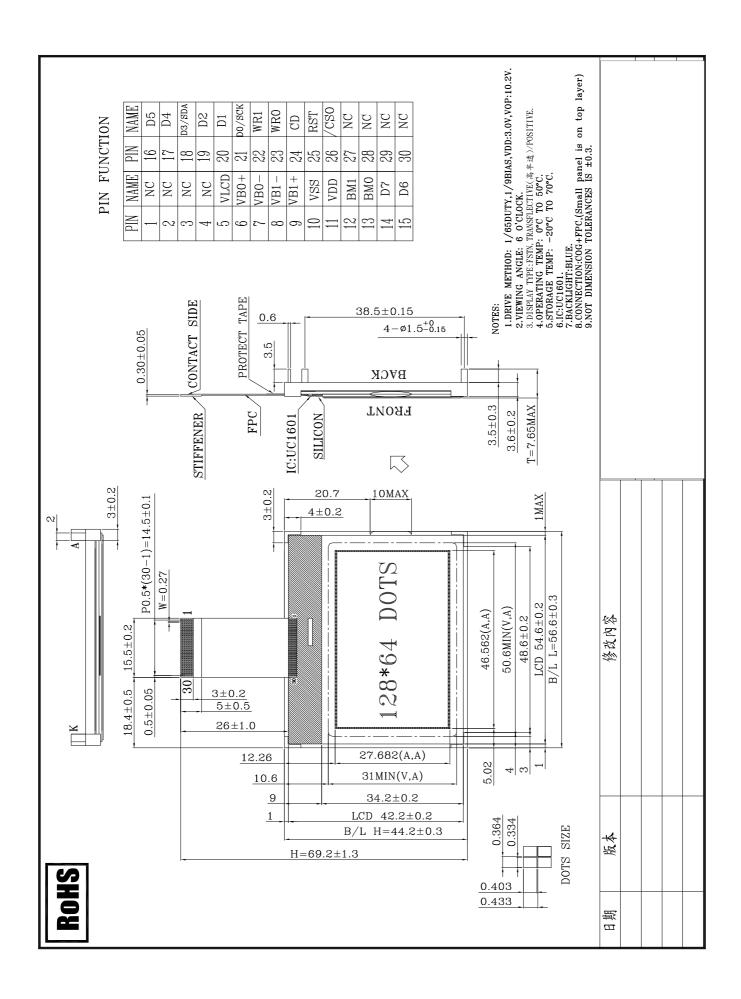

#### 2.2 Mechanical Characteristics

| Item                                                      | Characteristic          |

|-----------------------------------------------------------|-------------------------|

| Dot configuration                                         | 128 �64                 |

| Dot dimensions(mm)                                        | 0.334 \$0.403           |

| Dot spacing (mm)                                          | 0.364 �0.433            |

| Module dimensions (Horizontal & Vertical & Thickness, mm) | 56.6 \$44.2 \$7.65 max. |

| Viewing area (Horizontal ❖ Vertical, mm)                  | 50.6 �31                |

| Active area (Horizontal &Vertical, mm)                    | 46.562 \$27.682         |

2.3 Absolute

Maximum

Ratings

(Without LED

back-light)

| Characteristic            | Symbol                     | Unit | Value                        |

|---------------------------|----------------------------|------|------------------------------|

| Operating Voltage (logic) | $ m V_{DD}$                | V    | -0.3 to +4.0                 |

| Input Voltage             | $\mathbf{V}_{\mathbf{IN}}$ | V    | -0.3 to V <sub>DD</sub> +0.3 |

Note 1: Referenced to V<sub>SS</sub>=0V

### 2.4 Electrical Characteristics (Without LED back-light)

| Symbol               | Parameter                  | Conditions                                       | Min.               | Тур. | Max.               | Unit |

|----------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| Vod                  | Supply for digital circuit |                                                  | 2.4                |      | 3.3                | V    |

| V <sub>DD2/3</sub>   | Supply for bias & pump     |                                                  | 2.4                |      | 3.3                | V    |

| $V_{LCD}$            | Charge pump output         | $V_{DD2/3} \ge 2.4 \text{V}, 25^{\circ}\text{C}$ |                    |      | 11.5               | V    |

| V <sub>D</sub>       | LCD data voltage           | $V_{DD2/3} \ge 2.4V, 25^{\circ}C$                | 0.80               |      | 1.32               | V    |

| VIL                  | Input logic LOW            |                                                  |                    |      | 0.2V <sub>DD</sub> | V    |

| VIH                  | Input logic HIGH           |                                                  | 0.8V <sub>DD</sub> |      |                    | V    |

| Vol                  | Output logic LOW           |                                                  |                    |      | 0.2V <sub>DD</sub> | V    |

| Voн                  | Output logic HIGH          |                                                  | 0.8Vpp             |      |                    | V    |

| l <sub>ΙL</sub>      | Input leakage current      |                                                  |                    |      | 1.5                | μΑ   |

| R <sub>0(SEG)</sub>  | SEG output impedance       | V <sub>LCD</sub> = 11V                           |                    | 2    | 3                  | kΩ   |

| R <sub>0</sub> (COM) | COM output impedance       | V <sub>LCD</sub> = 11V                           |                    | 2    | 3                  | kΩ   |

| $F_{FR}$             | Average Frame Rate         | LC[3] = 0b                                       | 66                 | 76   |                    | Hz   |

### 2.5 Optical Characteristics Absolute maximum ratings

| Item | Symbol | Rating | Unit |

|------|--------|--------|------|

|      |        |        |      |

| Operating temperature range | Тор | 0~50   | ФC |

|-----------------------------|-----|--------|----|

| Storage temperature range   | Tst | -20~70 | ФC |

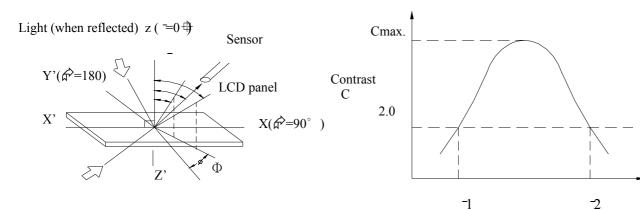

### 2.6 Optical Characteristics

1/65 duty, 1/9bias, Vop=10.2V, Ta=25°C

| Item                | Symbol     | Conditions                            | Min. | Тур. | Max   | Reference   |

|---------------------|------------|---------------------------------------|------|------|-------|-------------|

| Driving voltage     | Vop=VDD-VO |                                       |      | 10.2 |       |             |

| Viewing angle       | -          | C≥2.0,♠=0€€                           | 30⊕  |      |       | Notes 1 & 2 |

| Contrast            | С          | -=5 <del>\$</del> <b>\$</b> =0 ⊕      | 3.0  |      |       | Note 3      |

| Response time(rise) | ton        | -=5 <del>\$</del> \$\div \div =0 \div |      |      | 198ms | Note 4      |

| Response time(fall) | toff       | -=5 <del>\$</del> <b>\$</b> =0 ⊕      |      |      | 176ms | Note 4      |

Note 1: Definition of angles ⁻and ♠

Note 2: Definition of viewing angles ¬1 and ♠2

Light (when transmitted )  $Y(\overrightarrow{R}=0^{\circ})$  (  $=90^{\circ}$  )

Note: Optimum viewing angle with the naked eye and viewing angle -at Cmax. Above are not always the same

viewing angle  $\neg(\Phi \text{ fixed})$

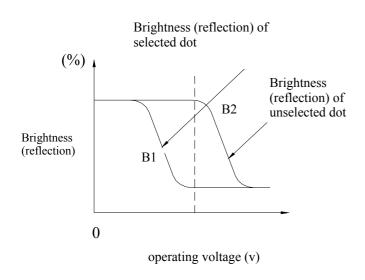

Note 3: Definition of contrast C

Brightness (reflection) of unselected dot (B2)

C = \_\_\_\_

Brightness (reflection) of selected dot (B1)

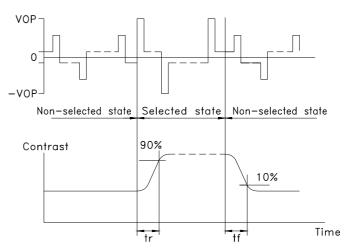

Note 4: Definition of response time

Note: Measured with a transmissive LCD panel which is displayed 1 cm<sup>2</sup>

$V_{\mbox{ OPR}}$  : Operating voltage  $$f_{\mbox{ FRM}}$$  : Frame frequency

$t_{ON}$ : Response time (rise)  $t_{OFF}$ : Response time (fall)

### 2.7 LED Back-light Characteristics

#### 2.7.1 Electrical / optical specifications

Ta = 25 €€

| Item                    | Symbol           | Condition        | Min. | Typ. | Max. | Unit  |

|-------------------------|------------------|------------------|------|------|------|-------|

| Forward voltage         | $V_{\mathrm{f}}$ | If=40mA,<br>BLUE | 2.9  | 3.2  | 3.6  | V     |

| LED *Luminous Intensity | $I_{ m V}$       | If=40mA,<br>BLUE |      | 120  |      | Cd/m2 |

| Reverse Current         | $I_R$            | VR=5V,<br>BLUE   |      |      | 0.1  | mA    |

Note: \*

Measured at

the bare

LED backlight unit.

#### 2.7.2 LED Maximum Operating Range

| Item              | Symbol           | BLUE | Unit |

|-------------------|------------------|------|------|

| Power Dissipation | $P_{AD}$         | 144  | mW   |

| Forward Current   | $I_{\mathrm{F}}$ | 40   | mA   |

| Reverse Voltage   | $V_R$            | 5    | V    |

# 3. RELIABILITY

# 3.1 Reliability

| Test item                                  | Test condition                                                                                        | Evaluation and assessment                       |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Operation at high temperature and humidity | 40 °C ⊕2 °C 90%RH for 500hours                                                                        | No abnormalities in functions* and appearance** |

| Operation at high temperature              | 50°C⊕2°C for 500 hours                                                                                | No abnormalities in functions* and appearance** |

| Heat shock                                 | 0 ⊕~ +50 °C Left for 1 hour<br>at each temperature,<br>transition time 5 min,<br>repeated 10times     | No abnormalities in functions* and appearance** |

| Low temperature                            | 0⊕2°C for 500 hours                                                                                   | No abnormalities in functions* and appearance** |

| Vibration                                  | Sweep for 1 min at 10 Hz,<br>55Hz, 10Hz, amplitude<br>1.5mm 2 hrs each in the<br>X,Y and Z directions | No abnormalities in functions* and appearance** |

| Drop shock                                 | Dropped onto a board from a height of 10cm                                                            | No abnormalities in functions* and appearance** |

<sup>\*</sup> Dissipation current, contrast and display functions

# 3.2 Liquid crystal panel service life

<sup>\*\*</sup> Polarizing filter deterioration, other appearance defects

100,000 hours minimum at 25 °C ⊕10 °C

- 3.3 definition of panel service life

- Contrast becomes 30% of initial value

- Current consumption becomes three times higher than initial value

- Remarkable alignment deterioration occurs in LCD cell layer

- Unusual operation occurs in display functions

### 4. OPERATING INSTRUCTIONS

# 4.1 Input signal Function

| Pin No | Symbol       | I/O |                           | Function                                                       |                    |                        |  |

|--------|--------------|-----|---------------------------|----------------------------------------------------------------|--------------------|------------------------|--|

| 1~4    | NC           | ı   | No Conr                   | No Connection.                                                 |                    |                        |  |

| 5      | <b>V</b> LCD | PWR | Main LC                   | Main LCD power supply.                                         |                    |                        |  |

| 6      | <b>V</b> B0+ | PWR | LCD Bia                   | LCD Bias Voltages. These are the voltage sources to provide    |                    |                        |  |

| 7      | <b>V</b> B0- | PWR | SEG driv                  | SEG driving currents. These voltages are generated internally  |                    |                        |  |

| 8      | <b>V</b> B1- | PWR | Connect                   | capacitors of C                                                | BX value betweer   | n VBX+ and VBX         |  |

| 9      | <b>V</b> B1+ | PWR |                           |                                                                |                    |                        |  |

| 10     | VSS          | PWR | Power G                   | round.                                                         |                    |                        |  |

| 11     | VDD          | PWR | Power s                   | upply terminal V                                               | CC.                |                        |  |

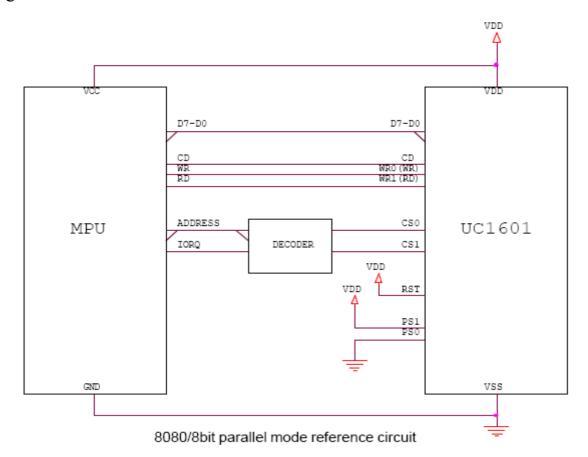

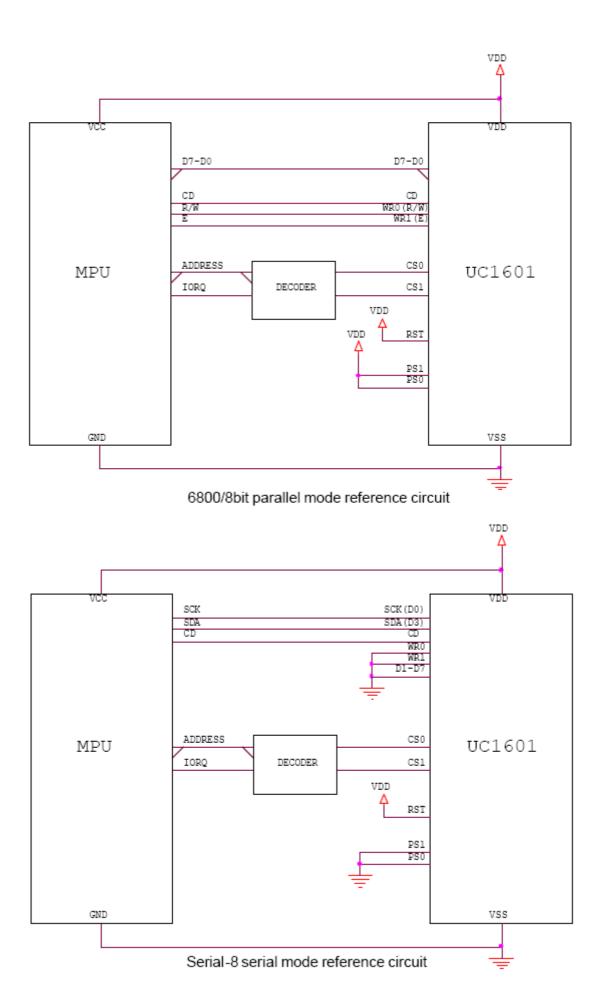

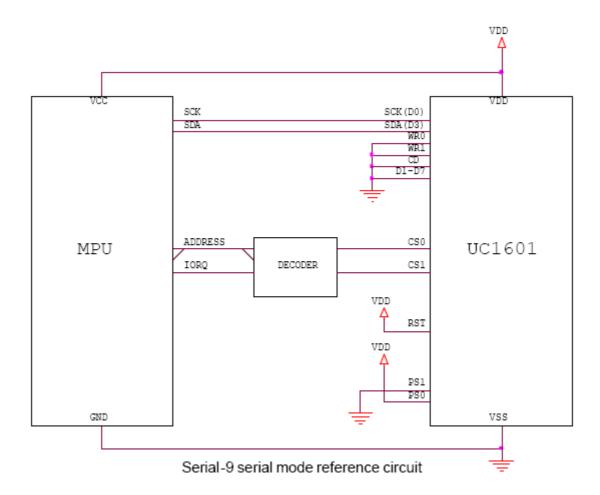

| 12     | BM1          | I   | Bus mod                   | Bus mode: "HL": 8080 "HH": 6800                                |                    |                        |  |

| 13     | ВМ0          | I   | BM[1:0] "LH": S9 "LL": S8 |                                                                |                    |                        |  |

| 14     | DB7          | I/O | Bi-direct                 | ional bus for bo                                               | th serial and par  | allel host interfaces. |  |

| 15     | DB6          | I/O | In serial                 | modes, connect                                                 | DB0 to SCK, DB     | 3 to SDA.              |  |

| 16     | DB5          | I/O |                           | BM=1x                                                          | BM=0x              |                        |  |

| 17     | DB4          | I/O |                           | (Parallel)                                                     | (Serial)           |                        |  |

| 18     | DB3/SDA      | I/O | D0<br>D1                  | D0<br>D1                                                       | SCK                |                        |  |

| 19     | DB2          | I/O | D2                        | D2                                                             |                    |                        |  |

| 20     | DB1          | I/O | D3<br>D4                  | D3                                                             | SDA                |                        |  |

| 21     | DB0/SCK      | I/O | D4                        | D4<br>D5                                                       |                    |                        |  |

|        |              |     | D6                        | D6                                                             | -                  |                        |  |

|        |              |     | D7                        | D7                                                             | -                  |                        |  |

| 22     | WR1          | I   | WR [1:0]                  | controls the rea                                               | d/write operatio   | n of the host          |  |

| 23     | WR0          | I   | interface                 | e. See Host Interf                                             | face section for o | details. The meaning   |  |

|        |              |     | of WR [1                  | :0] depends on v                                               | whether the inter  | face is in the 6800    |  |

|        |              |     | mode, o                   | r the 8080 mode.                                               | In serial modes    | , these two pins are   |  |

|        |              |     | not used                  | l and can be con                                               | nected to Vss.     |                        |  |

| 24     | CD           | I   | Select th                 | Select the incoming command if it is a control instruction or  |                    |                        |  |

|        |              |     | •                         | for display data. CD pin is not used in S9 mode, connect it to |                    |                        |  |

|        |              |     | Vdd or Vss.               |                                                                |                    |                        |  |

|        |              |     | " L": co                  | ntrol instruction                                              | "H": display d     | ata                    |  |

| 25     | RST          | I   | When R                    | ST="L", all contr                                              | ol registers are r | e-initialized by their |  |

|       |      |   | default states.                                                                                                 |

|-------|------|---|-----------------------------------------------------------------------------------------------------------------|

| 26    | /CS0 | ı | Chip Select or Chip Address. In parallel mode and S8 mode, chip is selected when /CS0="L". When the chip is not |

|       |      |   | selected, DB[7:0] will be high impedance.                                                                       |

| 27~30 | NC   | = | No Connection.                                                                                                  |

| В         | us Type | 8080        | 6800         | SPI (S8) | SPI (S9) |

|-----------|---------|-------------|--------------|----------|----------|

| "         | BM[1:0] | 10b         | 11b          | 00b      | 01b      |

| Pins      | CS[1:0] |             | Chip         | Select   |          |

| Data F    | CD      |             | Control/Data |          | _        |

| & Da      | WR0     | WR          | R/W          | -        | _        |

| Control 8 | WR1     | RD          | EN           | -        | _        |

| ,<br>ou   | Access  | Read        | Write        | Write    | Only     |

| 0         | D[7:0]  | 8-bit bus ( | (Tri-state)  | D0=SCK   | , D3=SDA |

<sup>\*</sup> Connect unused control pins and data bus pins to V<sub>DD</sub> or V<sub>SS</sub>

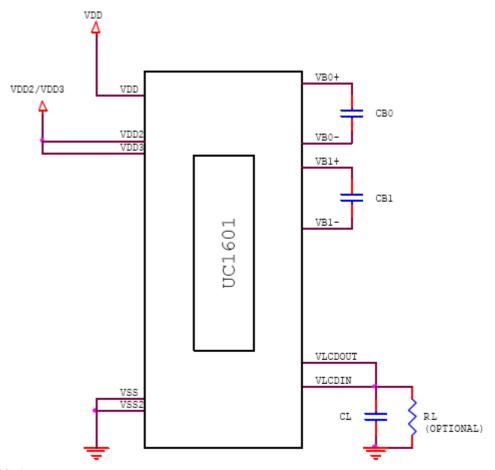

# 4.2 Voltage Generator Circuit

#### Note

Recommended component values:

C<sub>B</sub>: 100x~200x LCD load capacitance or 1.0uF (2V), whichever is higher.

$C_L$ : 10nF ~ 30nF (25V) is appropriate for most applications.

$R_L\colon\ 10M\Omega$  , Acts as a draining circuit when the power is abnormally shut down,

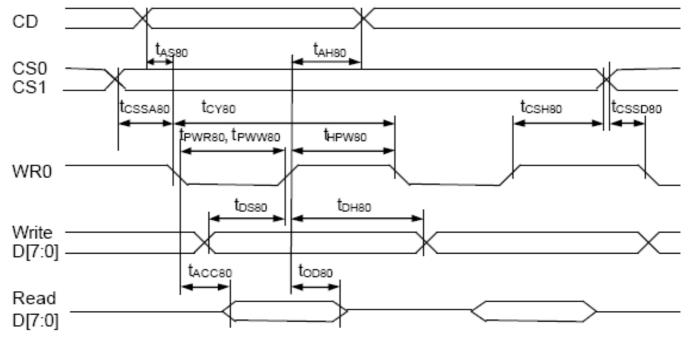

### 4.3 Timing Diagram

Parallel Bus Timing Characteristics (for 8080 MCU)

$(2.5V \le V_{DD} < 3.3V, Ta = -30 \text{ to } +85\degree\text{C})$

| Symbol             | Signal   | Description            | Condition              | Min. | Max. | Units |

|--------------------|----------|------------------------|------------------------|------|------|-------|

| taseo              | CD       | Address setup time     |                        | 0    | -    | nS    |

| t <sub>ahbo</sub>  | CD       | Address hold time      |                        | 40   |      |       |

| t <sub>CY80</sub>  |          | System cycle time      |                        | 135  | -    | nS    |

| t <sub>PWR80</sub> | WR1      | Pulse width (read)     |                        | 65   | -    | nS    |

| t <sub>PWW80</sub> | WR0      | Pulse width (write)    |                        | 65   | -    | nS    |

| t <sub>HPW80</sub> | WR0, WR1 | High pulse width       |                        | 65   | -    | nS    |

| t <sub>DS80</sub>  | D0~D7    | Data setup time        |                        | 30   | -    | nS    |

| t <sub>DH80</sub>  | D0~D1    | Data hold time         |                        | 20   |      |       |

| t <sub>ACC80</sub> |          | Read access time       | C <sub>L</sub> = 100pF | _    | 50   | nS    |

| topso              |          | Output disable time    |                        | 10   | 50   |       |

| tcssa80            |          |                        |                        | 10   |      | nS    |

| tcsspeo            | CS1/CS0  | Chip select setup time |                        | 10   |      |       |

| t <sub>csH80</sub> |          |                        |                        | 20   |      |       |

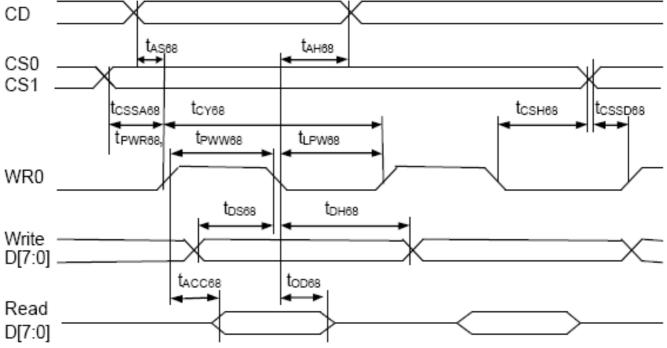

Parallel Bus Timing Characteristics (for 6800 MCU)

$(2.5V \le V_{DD} < 3.3V, Ta = -30 \text{ to } +85^{\circ}C)$

| Symbol              | Signal  | Description            | Condition              | Min. | Max. | Units |

|---------------------|---------|------------------------|------------------------|------|------|-------|

| t <sub>aseb</sub>   | CD      | Address setup time     |                        | 0    | -    | nS    |

| t <sub>ah68</sub>   |         | Address hold time      |                        | 40   |      |       |

| t <sub>CY68</sub>   |         | System cycle time      |                        | 135  | -    | nS    |

| t <sub>PWR68</sub>  | WR1     | Pulse width (read)     |                        | 65   | -    | nS    |

| t <sub>PWW68</sub>  |         | Pulse width (write)    |                        | 65   | -    | nS    |

| tlpw68              |         | Low pulse width        |                        | 65   | -    | nS    |

| t <sub>DS88</sub>   | D0~D7   | Data setup time        |                        | 30   | -    | nS    |

| tонвя               |         | Data hold time         |                        | 15   |      |       |

| t <sub>ACC88</sub>  |         | Read access time       | C <sub>L</sub> = 100pF | _    | 50   | nS    |

| t <sub>opes</sub>   |         | Output disable time    |                        | 10   | 50   |       |

| Tcssa68             | CS1/CS0 |                        |                        | 10   |      | nS    |

| T <sub>CSSD68</sub> |         | Chip select setup time |                        | 10   |      |       |

| T <sub>CSH88</sub>  |         |                        |                        | 20   |      |       |

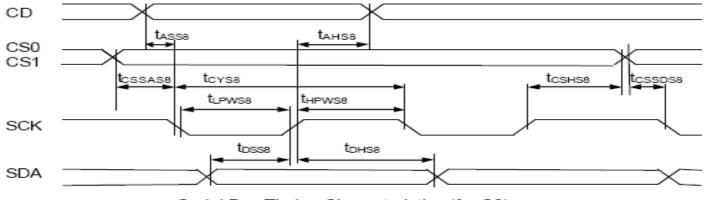

Serial Bus Timing Characteristics (for S8)

$(2.5V \le V_{DD} < 3.3V, Ta = -30 \text{ to } +85^{\circ}C)$

| Symbol             | Signal  | Description            | Condition | Min.     | Max. | Units |

|--------------------|---------|------------------------|-----------|----------|------|-------|

| t <sub>ass</sub>   | CD      | Address setup time     |           | 0        | _    | nS    |

| t <sub>ahs8</sub>  | CD      | Address hold time      |           | 40       | _    | nS    |

| t <sub>CYS8</sub>  |         | System cycle time      |           | 135      | _    | nS    |

| t <sub>LPWS8</sub> | SCK     | Low pulse width        |           | 65       | _    | nS    |

| t <sub>HPWS8</sub> |         | High pulse width       |           | 65       | _    | nS    |

| tossa              | SDA     | Data setup time        |           | 30       | _    | nS    |

| t <sub>DHS8</sub>  | SDA     | Data hold time         |           | 15       |      |       |

| tcssas8            |         |                        |           | 10       |      | nS    |

| tcssps8            | CS1/CS0 | Chip select setup time |           | 10<br>20 |      |       |

| tcsHs8             |         |                        |           | ∠0       |      |       |

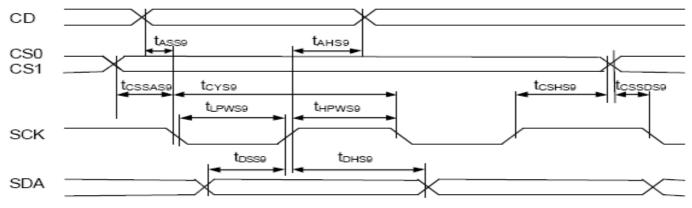

Serial Bus Timing Characteristics (for S9)

$$(2.5V \le V_{DD} < 3.3V, Ta = -30 \text{ to } +85^{\circ}C)$$

| Symbol                       | Signal  | Description                       | Condition | Min.           | Max. | Units |

|------------------------------|---------|-----------------------------------|-----------|----------------|------|-------|

| tasse                        | CD      | Address setup time                |           | 0              | _    | nS    |

| t <sub>AHS9</sub>            | OD      | Address hold time                 |           | 40             | _    | nS    |

| t <sub>CYS9</sub>            |         | System cycle time                 |           | 135            | _    | nS    |

| t <sub>LPWS9</sub>           | SCK     | Low pulse width                   |           | 65             | _    | nS    |

| t <sub>HPWS9</sub>           |         | High pulse width                  |           | 65             | _    | nS    |

| tosse<br>touse               | SDA     | Data setup time<br>Data hold time |           | 30<br>15       | -    | nS    |

| tcssase<br>tcsspse<br>tcsase | CS1/CS0 | Chip select setup time            |           | 10<br>10<br>20 |      | nS    |

### 5. NOTES

### **Safety**

PAGE 15/17

• If the LCD panel breaks, be careful not to get the liquid crystal in your mouth. If the liquid crystal touches your skin or clothes, wash it off immediately using soap and plenty of water.

#### **Handling**

- Avoid static electricity as this can damage the CMOS LSI.

- The LCD panel is plate glass; do not hit or crush it.

- Do not remove the panel or frame from the module.

- The polarizing plate of the display is very fragile; handle it very carefully

#### Mounting and Design

- Mount the module by using the specified mounting part and holes.

- To protect the module from external pressure, leave a small gap by placing transparent plates (e.g. acrylic or glass) on the display surface, frame, and polarizing plate

- Design the system so that no input signal is given unless the power-supply voltage is applied.

- Keep the module dry. Avoid condensation, otherwise the transparent electrodes may break.

#### **Storage**

- Store the module in a dark place where the temperature is 25 °C ⊕10 °C and the humidity below 65% RH.

- Do not store the module near organic solvents or corrosive gases.

- Do not crush, shake, or jolt the module (including accessories).

#### Cleaning

- Do not wipe the polarizing plate with a dry cloth, as it may scratch the surface.

- Wipe the module gently with soft cloth soaked with a petroleum benzine.

- Do not use ketonic solvents (ketone and acetoe) or aromatic solvents (toluene and xylene), as they may damage the polarizing plate.

#### 6. OPERATION PRECAUTIONS

Any changes that need to be made in this specification or any problems arising from it will be dealt with quickly by discussion between both companies.

#### 7. LCM Dimension